### ATA Flash card

WEDC ATA10 Series (ATA10) flash memory cards are ATA compatible cards and are suitable for usage as a data storage memory medium for PC's or any other electronic equipment.

Packaged in a PCMCIA type I or type II housing, the WEDC ATA series cards provide a lightweight, low power, reliable nonvolatile storage medium.

Built in to the card controller, Error Correcting Code (ECC) provides a high level of reliability and MTBF (Mean Time Between Failures)

WEDC's standard cards are shipped with the WEDC FLASH Logo. Cards are also available with blank housings (no Logo). The blank housings are available in both a recessed (for label) and flat housing. Please contact your WEDC sales representative for further information on Custom artwork.

### **Features**

• PC Card ATA compatible

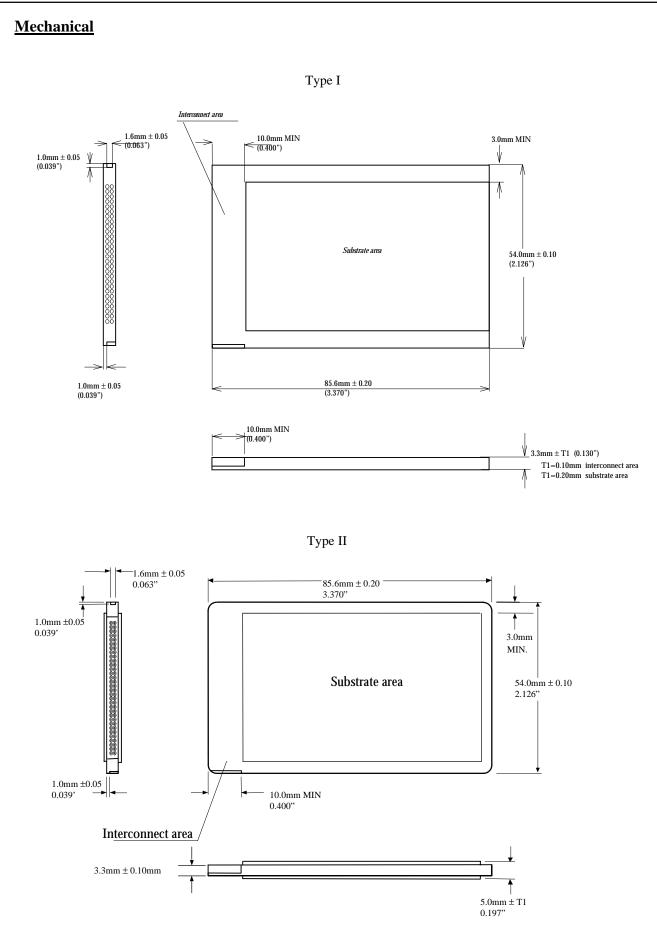

- 68 pin two piece connector and type I or type II housing (5mm)

- PCMCIA/JEIDA 4.1

- x8/x16 PCMCIA standard interface

- Single 3 Volt / 5 Volt Supply

- ISA standard, Read/Write unit is 1 sector (512 bytes) - Sector Read/Write transfer rate: 8 MB/s burst

- High reliability based on internal ECC function (Error Correcting Code) and wear leveling functions.

• Card Capacity - 8 MB to 512 MB (unformatted)

- Card Access mode:

- Memory card mode

- I/O card mode

- True-IDE mode

- Data Write Endurance is 100k program/erase cycles

- Data reliability is 1 error in 10<sup>14</sup> bits read

- Auto Sleep Function

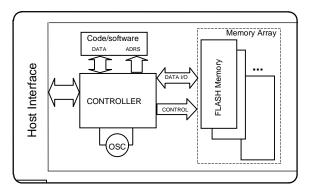

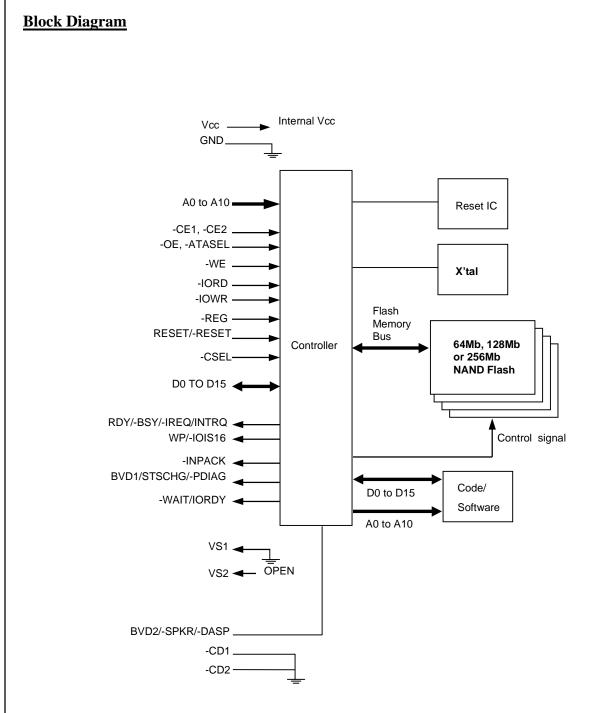

#### **Block Diagram**

# ATA10 Series

### **ATA10 Series**

## ATA10 Series

### **Card Capacity**

Because of card formatting, user available capacity is smaller than the original memory size. The table below presents the relation between card capacity and formatted capacity.

Note: Other capacities are available: contact your company sales representative for details.

|                 |          | Formatted |

|-----------------|----------|-----------|

| Card type       | Capacity | Capacity  |

| 7P008ATA1003C25 | 8MB      | 7.38MB    |

| 7P016ATA1003C25 | 16MB     | 15.42MB   |

| 7P032ATA1003C25 | 32MB     | 30.88MB   |

| 7P048ATA1003C25 | 48MB     | 47.23MB   |

| 7P064ATA1003C25 | 64MB     | 63.07MB   |

| 7P080ATA1003C25 | 80MB     | 76.00MB   |

| 7P096ATA1003C25 | 96MB     | 91.20MB   |

| 7P112ATA1003C25 | 112MB    | 106.40MB  |

| 7P128ATA1003C25 | 128MB    | 121.60MB  |

| 7P192ATA1003C25 | 192MB    | 183MB     |

| 7P256ATA1003C25 | 256MB    | 244MB     |

#### System Performance

| Item                           | Performance                           |

|--------------------------------|---------------------------------------|

| Data transfer rate             | 8.0 MB/s burst                        |

|                                | 1.0 MB/s sustained read               |

|                                | 600 kB/s sustained write              |

| Data reliability               | recoverable error in 10^14 bits read. |

| Start up time (Sleep to Idle)  | 2ms (max)                             |

| Start up time (Reset to Ready) | 50ms (typ)                            |

Card controller provides PCMCIA compatibility.

Card supports fast ATA host to buffer burst transfer rates up to 20MB/s (with PIO mode 4) and fast transfer rate to/from flash memory up to 8MB/s

### Absolute Maximum Ratings<sup>(1)</sup>

| Operating Temperature TA (ambient) |                       | <b>No</b> (1 |

|------------------------------------|-----------------------|--------------|

| Commercial                         | 0°C to +60 °C         | "A           |

| Industrial                         | -40°C to +85 °C       | pe           |

| Storage Temperature                |                       | st           |

| Commercial                         | -20°C to +85 °C       | th           |

| Industrial                         | -40°C to +85 °C       | th           |

| Voltage on any pin relative to VSS | -0.5V to VCC+0.5V (1) | of<br>to     |

| VCC supply Voltage relative to VSS | -0.5V to +7.0V        | l ex         |

#### e:

Stress greater than those listed under solute Maximum ratings" may cause manent damage to the device. This is a ess rating only and functional operation at se or any other conditions greater than se indicated in the operational sections nis specification is not implied. Exposure bsolute maximum rating conditions for ended periods may affect reliability.

#### **Recommended DC Operating Conditions**

| Parameter      | Symbol | Min |    | Max | Unit | Note |

|----------------|--------|-----|----|-----|------|------|

| Operating temp | Та     | 0   | 25 | 60  | С    |      |

| Vcc voltage    | Vcc    | 4.5 | 5  | 5.5 | V    |      |

# **DC Characteristics**<sup>(1)</sup>

CMOS Test Conditions: VIL = VSS ± 0.2V, VIH = VCC ± 0.2V

| Symbol | Parameter                 | Notes | Min  | Тур | Max  | Units | Test Conditions                  |

|--------|---------------------------|-------|------|-----|------|-------|----------------------------------|

| Vcc    | Power Supply Voltage      |       | 4.5V |     | 5.5V |       |                                  |

| ICC1   | Sector READ current       | 2     |      | 50  |      | mA    | CMOS level                       |

| ICC2   | Sector WRITE current      | 2     |      | 50  |      | mA    | CMOS level                       |

| ICCS   | VCC Sleep/Standby Current | 1, 2  |      | 0.5 |      | mA    | Control Signals = VCC            |

| ILI    | Input Leakage Current     | 1, 3  |      |     | ±20  | μA    | VCC = VCCMAX<br>Vin =VCC or VSS  |

| ILO    | Output Leakage Current    |       |      |     | ±20  | μA    | VCC = VCCMAX<br>Vout =VCC or VSS |

| VIL    | Input Low Voltage         |       |      |     | 0.8  | V     |                                  |

| VIH    | Input High Voltage        |       | 2.0  |     |      | V     |                                  |

| VOL    | Output Low Voltage        |       |      |     | 0.4  | V     | IOL = 3.2mA                      |

| VOH    | Output High Voltage       |       | 2.4  |     |      | V     | IOH = -2.0mA                     |

#### Notes:

1. Control Signals: CE1#, CE2#, OE#, WE#, REG#, IORD#, IOWR#.

2. Typical: VCC = 5V, T = +25C.

3. Exceptions: Leakage currents on control signals will be < 500 µA when VIN = GND due to internal pull-up resistors.

# <u>Pinout</u>

|            | Memory card mo | de  | I/O Card Mode   |     | True IDE Mode |     |

|------------|----------------|-----|-----------------|-----|---------------|-----|

| Pin Number | Signal Name    | I/O | Signal Name I/O |     | Signal Name   | I/O |

| 1          | GND            |     | GND             |     | GND           |     |

| 2          | D3             | I/O | D3              | I/O | D3            | I/O |

| 3          | D4             | I/O | D4              | I/O | D4            | I/O |

| 4          | D5             | I/O | D5              | I/O | D5            | I/O |

| 5          | D6             | I/O | D6              | I/O | D6            | I/O |

| 6          | D7             | I/O | D7              | I/O | D7            | I/O |

| 7          | CE1#           | Ι   | CE1#            | Ι   | CE1#          | Ι   |

| 8          | A10            | Ι   | A10             | Ι   | A10           | Ι   |

| 9          | OE#            | Ι   | OE#             | Ι   | ATASEL#       | Ι   |

| 10         | N.C.           | -   | N.C.            | -   | N.C.          | -   |

| 11         | A9             | Ι   | A9              | Ι   | A9            | Ι   |

| 12         | A8             | Ι   | A8              | Ι   | A8            | Ι   |

| 13         | N.C.           | -   | N.C.            | -   | N.C.          | -   |

| 14         | N.C.           | -   | N.C.            | -   | N.C.          | -   |

| 15         | WE#            | Ι   | WE#             | Ι   | WE#           | Ι   |

| 16         | RDY/BSY        | 0   | IREQ#           | 0   | INTRQ         | 0   |

| 17         | Vœ             |     | Vœ              |     | Vœ            |     |

| 18         | N.C.           | -   | N.C.            | -   | N.C.          | -   |

| 19         | N.C.           | -   | N.C.            | -   | N.C.          | -   |

| 20         | N.C.           | -   | N.C.            | -   | N.C.          | -   |

| 21         | N.C.           | -   | N.C.            | -   | N.C.          | -   |

| 22         | A7             | Ι   | A7              | Ι   | A7            | Ι   |

| 23         | A6             | Ι   | A6              | Ι   | A6            | Ι   |

| 24         | A5             | Ι   | A5              | Ι   | A5            | Ι   |

| 25         | A4             | Ι   | A4              | Ι   | A4            | Ι   |

| 26         | A3             | Ι   | A3              | Ι   | A3            | Ι   |

| 27         | A2             | Ι   | A2              | Ι   | A2            | Ι   |

| 28         | A1             | Ι   | A1              | Ι   | A1            | Ι   |

| 29         | A0             | Ι   | A0              | Ι   | A0            | Ι   |

| 30         | D0             | I/O | D0              | I/O | D0            | I/O |

| 31         | D1             | I/O | D1              | I/O | D1            | I/O |

| 32         | D2             | I/O | D2              | I/O | D2            | I/O |

| 33         | WP             | 0   | IOIS16#         | 0   | IOIS16#       | 0   |

| 34         | GND            |     | GND             |     | GND           |     |

# Pinout (Cont.)

|            | Memory card mo | de  | I/O Card Mode   |     | True IDE Mode |     |

|------------|----------------|-----|-----------------|-----|---------------|-----|

| Pin Number | Signal Name    | I/O | Signal Name I/O |     | Signal Name   | I/O |

| 35         | GND            |     | GND             |     | GND           |     |

| 36         | CD1#           | 0   | CD1#            | 0   | CD1#          | 0   |

| 37         | D11            | I/O | D11             | I/O | D11           | I/O |

| 38         | D12            | I/O | D12             | I/O | D12           | I/O |

| 39         | D13            | I/O | D13             | I/O | D13           | I/O |

| 40         | D14            | I/O | D14             | I/O | D14           | I/O |

| 41         | D15            | Ι   | D15             | Ι   | D15           | Ι   |

| 42         | CE2#           | Ι   | CE2#            | Ι   | CE2#          | Ι   |

| 43         | VS1            | 0   | VS1             | 0   | VS1           | 0   |

| 44         | IORD#          | Ι   | IORD#           | Ι   | IORD#         | Ι   |

| 45         | IOWR#          | Ι   | IOWR#           | Ι   | IOWR#         | Ι   |

| 46         | NC             | -   | NC              | -   | NC            | -   |

| 47         | NC             | -   | NC              | -   | NC            | -   |

| 48         | NC             | -   | NC              | -   | NC            | -   |

| 49         | NC             | -   | NC              | -   | NC            | -   |

| 50         | NC             | -   | NC              | -   | NC            | -   |

| 51         | Vcc            |     | Vcc             |     | Vcc           |     |

| 52         | NC             | -   | NC              | -   | NC            | -   |

| 53         | NC             | -   | NC              | -   | NC            | -   |

| 54         | NC             | -   | NC              | -   | NC            | -   |

| 55         | NC             | -   | NC              | -   | NC            | -   |

| 56         | CSEL#          | Ι   | CSEL#           | Ι   | CSEL#         | Ι   |

| 57         | VS2            | 0   | VS2             | 0   | VS2           | 0   |

| 58         | RESET          | Ι   | RESET           | Ι   | RESET#        | Ι   |

| 59         | Wait#          | 0   | Wait#           | 0   | IORDY         | 0   |

| 60         | INPACK#        | 0   | INPACK#         | 0   | INPACK#       | 0   |

| 61         | REG#           | Ι   | REG#            | Ι   | REG#          | Ι   |

| 62         | BVD2           | I/O | SPKR#           | I/O | DASP          | I/O |

| 63         | BVD1           | I/O | STSCHG#         | I/O | PDIAG#        | I/O |

| 64         | D8             | I/O | D8              | I/O | D8            | I/O |

| 65         | D9             | I/O | D9              | I/O | D9            | I/O |

| 66         | D10            | 0   | D10             | 0   | D10           | 0   |

| 67         | CD2#           | 0   | CD2#            | 0   | CD2#          | 0   |

| 68         | GND            |     | GND             |     | GND           |     |

Note: CD1# and CD2# are grounded internal to PC Card.

# **Card Signal Description**

| Symbol                       | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 – A10                     | INPUT            | <b>ADDRESS INPUTS:</b> A0 through A10 Signal A0 is not used in word access mode. A10 is the most significant bit. In True IDE Mode only HA[20] are used for selecting the eight registers in the Task File, the remaining address lines should be grounded.                                                                                                                                                                                                                                                          |

| D0 - D15                     | INPUT/OUT<br>PUT | <b>DATA INPUT/OUTPUT:</b> D0 THROUGH D15 constitute the bi-<br>directional databus. D0 - D7 constitute the lower (even) byte and D8 -<br>D15 the upper (odd) byte. D15 is the MSB.                                                                                                                                                                                                                                                                                                                                   |

| C E1 #, C E2 #               | INPUT            | <b>CARD ENABLE 1 AND 2:</b> active low signals; CE1 # enables even<br>byte accesses, CE2 # enables odd byte accesses. In True IDE Mode<br>CE2 # is used to select the Alternate Status Register and the Device<br>control Register while CE1 # is the cheap select for the other task file<br>registers.                                                                                                                                                                                                             |

| OE#,<br>ASTEL#               | INPUT            | <b>OUTPUT ENABLE, ATA Select:</b> Active low signal enabling read data from Attribute and Common memory area. To enable True IDE Mode this input should be grounded by the host.                                                                                                                                                                                                                                                                                                                                     |

| WE#                          | INPUT            | <b>WRITE ENABLE:</b> Active low signal gating write data to the memory card. In true IDE Mode this input signal is not used and should be connected to Vcc.                                                                                                                                                                                                                                                                                                                                                          |

| RDY/BSY #<br>IREQ #<br>INTRQ | OUTPUT           | <b>Ready/Busy, Interrupt Request:</b> In I/O mode this signal is is<br>IREQ # pin. The signal of low level indicates that the card is requesting<br>software service to host, and high level indicate that the card is not<br>requesting. In memory mode, the signal is set high when the ATA card<br>is ready to accept new data transfer operation and held low when card<br>is busy.<br>At power up and at Reset, the RDY/BSY is low until (busy) until the<br>card has completed its power up or reset function. |

| CD1 #, CD2 #                 | OUTPUT           | Host should provide a pull up resistor<br>CARD DETECT 1 and 2: Provide card insertion detection. These<br>signals are connected to ground internally on the memory card. The<br>host socket interface circuitry shall supply 10K-ohm or larger pull-up<br>resistors on these signal pins.                                                                                                                                                                                                                            |

| WP<br>IOIS16#                | OUTPUT           | Write Protect, 16 bit I/O port: In memory mode, WP is held low:<br>always writable). In I/O mode, IOIS16 # is asserted low when Task<br>File Registers are accessed in 16 bit mode. In True IDE mOde this<br>signal is asserted low when this device is expecting a word data transfer<br>cycle.                                                                                                                                                                                                                     |

| VPP1, VPP2                   | N.C.             | <b>PROGRAM/ERASE POWER SUPPLY:</b> No Connection for ATA card.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VCC                          |                  | <b>CARD POWER SUPPLY:</b> 5.0V for all internal circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND                          |                  | <b>GROUND:</b> for all internal circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REG #                        | INPUT            | <b>ATTRIBUTE MEMORY SELECT:</b> Used to enable access to<br>Attribute space. Should be in high level during common memory area<br>access. In True IDE Mode input signal is not used and should be<br>connected to Vcc.                                                                                                                                                                                                                                                                                               |

| Reset<br>Reset #             | INPUT            | <b>Reset, Reset #:</b> Active signal will clear all registers on the card (power on default). In True IDE Mode Reset # is the active low hardware reset from the host.                                                                                                                                                                                                                                                                                                                                               |

# **Card Signal Description (Cont.)**

| Symbol                       | Туре         | Name and Function                                                                                                                                                                                                                                                                                                                               |

|------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT #                       | OUTPUT       | <b>WAIT:</b> This signal outputs low level for purpose of delaying memory or I/O access cycle. In True IDE Mode this signal can be used as IORDY.                                                                                                                                                                                               |

| BVD2<br>SPKR #<br>DASP #     | Input/Output | <b>Battery Voltage Detect 2, Data audio output, Disk active/slave</b><br><b>present:</b> In memory card mode, BVD2 is always high. In I/O mode,<br>SPKR # is held high: no digital audio signals. In True IDE Mode<br>DASP # is Disk Active/Slave Present signal in Master/Slave<br>handshake protocol.                                         |

| BVD1<br>STSCHNG #<br>PDIAG # | Input/Output | <b>Battery Voltage Detect 1, Status Change, Pass Diagnostic:</b> In<br>memory card mode BVD1 Is set to high level. In I/O mode<br>STSCHNG # is used to alert the host to changes in Status registers. In<br>True IDE mode PDIG is the Pass Diagnostic signal in Master/Slave<br>handshake protocol.                                             |

| VS1, VS2                     | OUTPUT       | <b>VOLTAGE SENSE:</b> Notifies the host socket of the card's VCC requirements. VS1 and VS2 are open to indicate a 5V, 16 bit card has been inserted.                                                                                                                                                                                            |

| CSEL #                       | Input        | <b>C ard Select:</b> This signal is not used in memory and I/O mode. With internal pull up resistor this signal is used to configure this card as Master or Slave when configured in True IDE Mode. When this pin is GND, selected Master config, when pin is open the card is configured as a Slave.                                           |

| INPACK#                      | Output       | <b>Input Acknowledge</b> : This signal is not used in memory mode. It is asserted by the card when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used for the input data buffer control. In True IDE Mode this signal is not used and should not be connected at the host. |

| IORD #                       | Input        | <b>I/O Read:</b> is used for control of read data in Task File area. This card respond to this signal only in I/O interface mode                                                                                                                                                                                                                |

| IOWR #                       | Input        | <b>I/O Write:</b> is used for control of data write in Task File area. This card respond to this signal only in I/O interface mode                                                                                                                                                                                                              |

#### **Card Function Explanation**

#### **Register Construction**

- Attribute Region

- Configuration Register

- Configuration Option Register

- Configuration and Status Register

- Pin Replacement Register

- Socket and Copy Register

- CIS (Card Information Structure)

- Task File Region

- Error Register

- Feature Register

- Sector Count Register

- Sector Number Register

- Cylinder Low Register

- Cylinder High Register

- Drive/Head Register

- Status Register

- Command Register

- Disk Address Pointer

- Buffer RAM Size Control Register

- Host Interrupt Status Register

- Host Interrupt Enable Register

- ECC Control Register

- ECC 0-2 Registers

- DMA Control Register

### **Host Access Specification**

#### 1. Attribute Access Specification

When the CIS-ROM region or Configuration register region is accessed, read and write operations are executed under the condition of REG# = Low as follows. That region can be accessed by Byte/Word/Odd-byte modes which are defined by the PC card standard specification.

#### Attribute Read Access Mode

| Mode                  | REG# | CE2# | CE1# | <b>A0</b> | OE# | WE# | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|-----------|-----|-----|----------|-----------|

| Standby Mode          | Х    | Н    | Н    | Х         | Х   | Х   | High Z   | High Z    |

| Byte access           | L    | Н    | L    | L         | L   | Н   | High Z   | even byte |

|                       | L    | Н    | L    | Н         | L   | Н   | High Z   | invalid   |

| Word access (16 bit)  | L    | L    | L    | Х         | L   | Н   | invalid  | even byte |

| Odd Byte access (8 bi | L    | L    | Н    | Х         | L   | Н   | invalid  | High Z    |

#### Attribute Write Access Mode

| Mode                  | REG# | CE2# | CE1# | <b>A0</b> | OE# | WE# | D15 - D8   | D7 - D0    |

|-----------------------|------|------|------|-----------|-----|-----|------------|------------|

| Standby Mode          | Х    | Н    | Н    | Х         | X   | Х   | Don't care | Don't care |

| Byte access           | L    | Н    | L    | L         | Н   | L   | Don't care | even byte  |

|                       | L    | Н    | L    | Н         | Н   | L   | Don't care | Don't care |

| Word access (16 bit)  | L    | L    | L    | Х         | Н   | L   | Don't care | even byte  |

| Odd Byte access (8 bi | L    | L    | Н    | Х         | Н   | L   | Don't care | Don't care |

#### 2. Task File Register Access Specification

There are two cases of Task File register mapping, one is the mapped I/O address area, the other is the Mapped Memory address area. Each case of the Task File register read and write operation is executed under the following conditions. The area can be accessed by Byte/Word/Odd Byte mode which is defined by the PC card standard specification.

#### (a) I/O address map

Task File Register Read Access Mode (a)

| Mode                  | REG# | CE2# | CE1# | <b>A0</b> | IORD# | IOWR# | OE# | WE# | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|-----------|-------|-------|-----|-----|----------|-----------|

| Standby Mode          | X    | Н    | Н    | Х         | Х     | Х     | Х   | Х   | High Z   | High Z    |

| Byte access           | L    | Н    | L    | L         | L     | Н     | Н   | Н   | High Z   | even byte |

|                       | L    | Н    | L    | Н         | L     | Н     | Н   | Н   | High Z   | odd byte  |

| Word access (16 bit)  | L    | L    | L    | Х         | L     | Н     | Н   | Н   | odd byte | even byte |

| Odd Byte access (8 bi | t L  | L    | Н    | Х         | L     | Н     | Н   | Н   | odd byte | High Z    |

Task File Register Write Access Mode (a)

| Mode                  | REG# | CE2# | CE1# | <b>A0</b> | IORD# | IOWR# | OE# | WE# | D15 - D8   | D7 - D0    |

|-----------------------|------|------|------|-----------|-------|-------|-----|-----|------------|------------|

| Standby Mode          | Х    | Н    | Н    | Х         | Х     | Х     | Х   | Х   | Don't care | Don't care |

| Byte access           | L    | Н    | L    | L         | Н     | L     | Н   | Н   | Don't care | even byte  |

|                       | L    | Н    | L    | Н         | Н     | L     | Н   | H   | Don't care | odd byte   |

| Word access (16 bit)  | L    | L    | L    | Х         | Н     | L     | Н   | Н   | odd byte   | even byte  |

| Odd Byte access (8 bi | L    | L    | Н    | Х         | Н     | L     | Н   | Н   | odd byte   | Don't care |

#### (b) Memory address map

Task File Register Read Access Mode (b)

| Mode                  | REG# | CE2# | CE1# | <b>A0</b> | IORD# | IOWR# | OE# | WE# | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|-----------|-------|-------|-----|-----|----------|-----------|

| Standby Mode          | Х    | Н    | Н    | Х         | Х     | Х     | Х   | Х   | High Z   | High Z    |

| Byte access           | Н    | Н    | L    | L         | Н     | н     | L   | Н   | High Z   | even byte |

|                       | Н    | Н    | L    | Н         | Н     | н     | L   | Н   | High Z   | odd byte  |

| Word access (16 bit)  | Н    | L    | L    | Х         | Н     | Н     | L   | Н   | odd byte | even byte |

| Odd Byte access (8 bi | H    | L    | Н    | Х         | Н     | Н     | L   | Н   | odd byte | High Z    |

Task File Register Write Access Mode (b)

| Mode                  | REG# | CE2# | CE1# | <b>A0</b> | IORD# | IOWR# | OE# | WE# | D15 - D8   | D7 - D0    |

|-----------------------|------|------|------|-----------|-------|-------|-----|-----|------------|------------|

| Standby Mode          | Х    | Н    | Н    | Х         | Х     | Х     | Х   | Х   | Don't care | Don't care |

| Byte access           | Н    | Н    | L    | L         | Н     | Н     | Н   | L   | Don't care | even byte  |

|                       | Н    | Н    | L    | Н         | Н     | Н     | Н   | L   | Don't care | odd byte   |

| Word access (16 bit)  | Н    | L    | L    | Х         | Н     | Н     | Н   | L   | odd byte   | even byte  |

| Odd Byte access (8 bi | Н    | L    | Н    | Х         | Н     | Н     | Н   | L   | odd byte   | Don't care |

#### 3. True IDE Mode

The card can be configured in a True IDE Mode of operation. This card is configured in this mode only when the OE# input signal is asserted low by the host during the power off to power on cycle. In this True IDE Mode the PCMCIA protocol and configuration are disabled and only an I/O operation to the Task File registers is allowed. In this mode no Memory or Attribute registers are accessible to the host. The card permits 8 bit access if the user issues a Set feature Command to put the device in the 8 bit Mode.

#### True IDE Mode Read I/O function

| Mode                   | CE2# | CE1# | A0A2 | IORD# | IOWR# | D15 - D8 | D7 - D0    |

|------------------------|------|------|------|-------|-------|----------|------------|

| Invalid Mode           | L    | L    | Х    | Х     | Х     | High Z   | High Z     |

| Standby Mode           | н    | Н    | Х    | Х     | Х     | High Z   | High Z     |

| Data Register Access   | Н    | L    | 0h   | L     | Н     | odd byte | even byte  |

| All status access      | L    | Н    | 6h   | L     | Н     | High Z   | status out |

| Other task file access | Н    | L    | 1-7h | L     | Н     | High Z   | data       |

#### True IDE Mode Read I/O function

| Mode                   | CE2# | CE1# | A0A2 | IORD# | IOWR# | D15 - D8   | D7 - D0    |

|------------------------|------|------|------|-------|-------|------------|------------|

| Invalid Mode           | L    | L    | Х    | Х     | Х     | Don't care | Don't care |

| Standby Mode           | Н    | Н    | Х    | Х     | Х     | Don't care | Don't care |

| Data Register Access   | Н    | L    | 0h   | Н     | L     | odd byte   | even byte  |

| All status access      | L    | Н    | 6h   | Н     | L     | Don't care | control in |

| Other task file access | Н    | L    | 1-7h | Н     | L     | Don't care | data       |

#### **Configuration Register Specifications**

This card supports four Configuration registers for the purpose of the configuration and observation of this card.

#### 1. Configuration Option Register (Address 200H)

This register is used for the configuration of the card configuration status and for the issuing the soft reset to the card.

| bit7   | bit6    | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |  |

|--------|---------|-------|------|------|------|------|------|--|

| SRESET | LevIREQ | INDEX |      |      |      |      |      |  |

Note: initial value: 00H

| Name                | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRESET<br>(HOST->)  | R/W | Setting this bit to "1", places the card in the reset state (Card Hard Reset). This operation is equal to Hard Reset, except this bit is not cleared. Then this bit is set to "0", places the card in the reset state of Hard Reset (This bit is set to "0" by Hard Reset). Card configuration status is reset and the card internal initialized operation starts when Card Hard Reset is executed, so the next access to the card should be the same sequence as the power on sequence. |

| LevIREQ<br>(HOST->) | R/W | This bit sets to "0" when pulse mode interrupt is selected, and "1" when level mode interrupt is selected.                                                                                                                                                                                                                                                                                                                                                                               |

| INDEX<br>(HOST->)   | R/W | This bit is used to select the operation mode of the card as follows.<br>When Power on, Card Hard Reset and Soft Reset, this data is "000000" for the purpose<br>of Memory card interface recognition.                                                                                                                                                                                                                                                                                   |

#### **INDEX** bit assignment

#### INDEX bit

| 5 | 4 | 3 | 2 | 1 | 0 | Card mode   | Task File register address | Mapping mode          |

|---|---|---|---|---|---|-------------|----------------------------|-----------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | Memory card | 0H to FH, 400H to 7FFH     | memory mapped         |

| 0 | 0 | 0 | 0 | 0 | 1 | I/O card    | xx0H to xxFH               | contiguous I/O mapped |

| 0 | 0 | 0 | 0 | 1 | 0 | I/O card    | 1F0H to 1F7H, 3F6H to 3F7H | primary I/O mapped    |

| 0 | 0 | 0 | 0 | 1 | 1 | I/O card    | 170H to 177H, 376H to 377H | secondary I/O mapped  |

#### 2. Configuration and Status Register (Address 202H)

This register is used for observing the card state.

| bit7  | bit6   | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------|--------|-------|------|------|------|------|------|

| CHGED | SIGCHG | IOIS8 | 0    | 0    | PWD  | INTR | 0    |

Note: initial value: 00H

| Name               | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHGED<br>(CARD->)  | R   | This bit indicates that the CRDY/-BSY bit on the Pin Replacement register is set to "1". When CHGED bit is set to "1", the -STSCHG pin is held "L" at the condition of SIGCHG bit set to "1" and the card configured for the I/O interface.                                                                                                                                                                                                   |

| SIGCHG<br>(HOST->) | R/W | This bit is set or reset by the host for enabling and disabling the status-change signal (-<br>STSCHG pin). When the card is configured I/O card interface and this bit is set to "1", -<br>STSCHG pin is controlled by the CHGED bit. If this bit is set to "0", the -STSCHG pin is<br>kept "H".                                                                                                                                             |

| IOIS8<br>(HOST->)  | R/W | The host sets this field to "1" when it can provide I/O cycles only with on 8 bit data bus (D7 to D0).                                                                                                                                                                                                                                                                                                                                        |

| PWD<br>(HOST->)    | R/W | When this bit is set to "1", the card enters the sleep state (Power Down mode). When this bit is reset to "0", the card transfers to the idle state (active mode). RRDY/-BSY bit on the Pin Replacement Register becomes BUSY when this bit is changed. RRDY/-BSY will not become Ready until the power state requested has been entered. This card automatically powers down when it is idle, and powers back up when it receives a command. |

| INTR<br>(CARD->)   | R   | This bit indicates the internal state of the interrupt request. This bit state is available whether the I/O card interface has been configured or not. This signal remains true until the condition which caused the interrupt request has been serviced. If interrupts are                                                                                                                                                                   |

disabled by the -IEN bit in the Device Control Register, this bit is a zero.

| t7                            | bit6              | bit5                               | bit4     | bit3        | bit2            | bit1                | bit0    |

|-------------------------------|-------------------|------------------------------------|----------|-------------|-----------------|---------------------|---------|

| 0                             | 0                 | CRDY/-BSY                          | 0        | 1           | 1               | RRDY/-BSY           | 0       |

|                               |                   |                                    |          |             |                 |                     |         |

| Manua                         |                   | Francisco                          |          |             |                 |                     |         |

| CRDY/-BSY                     | <b>R/W</b><br>R/W | Function<br>This bit is set to "1" | when the | RRDY/-BSY t | bit changes sta | ate. This bit may a | Ilso be |

| Name<br>CRDY/-BSY<br>(HOST->) |                   |                                    | when the | RRDY/-BSY t | oit changes sta | ate. This bit may a | llso be |

### 4. Socket and Copy Register (Address 206H)

This register is used for identification of the card from the other cards. The host can read and write this register. This register should be set by the host before this card's Configuration Option register set.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | 0    | DRV# | 0    | 0    | 0    | 0    |

Note: initial value: 00H

#### Name R/W Function

| DRV#     | R/W | This field is used for the configuration of the plural cards. |

|----------|-----|---------------------------------------------------------------|

| (HOST->) |     |                                                               |

### **Sector Transfer Protocol**

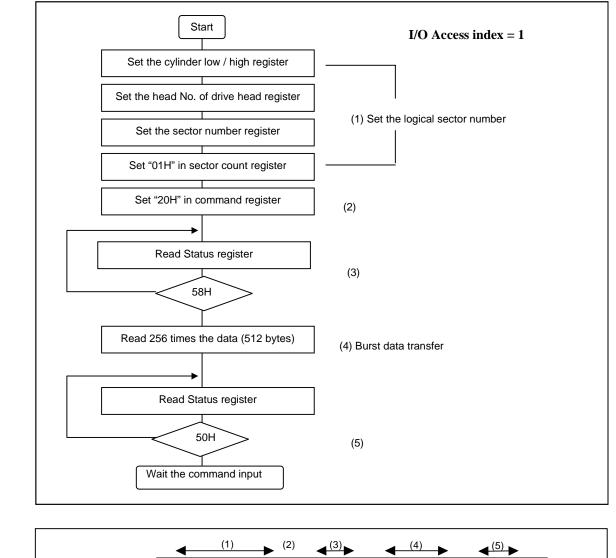

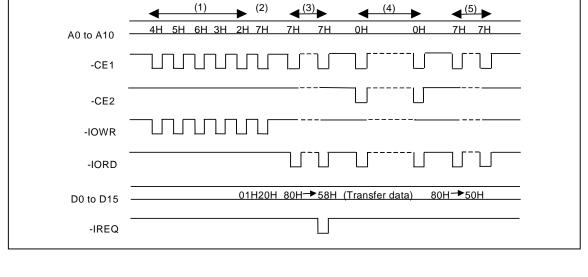

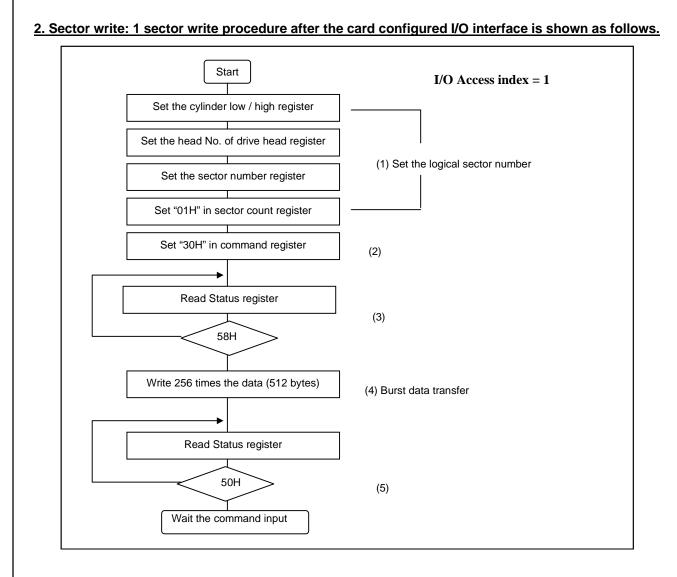

#### 1. Sector read: 1 sector read procedure after the card configured I/O interface is shown as follows.

### **ATA10 Series**

#### June 2000 Rev. 5 - ECO #12901

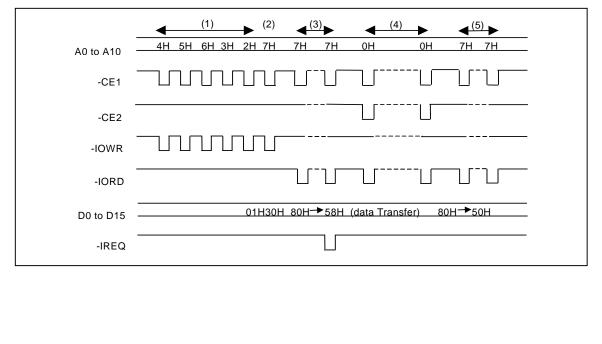

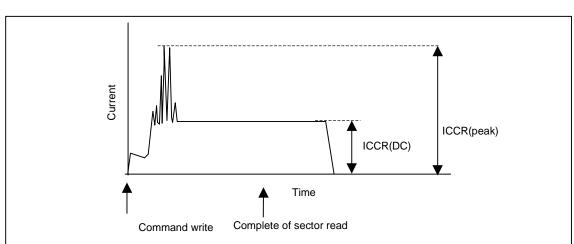

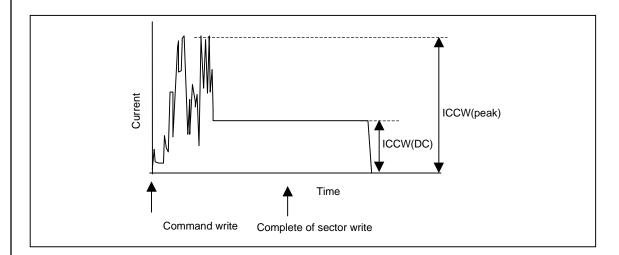

**DC Current Waveform** (Example of sector read or write:  $V_{CC} = 5 \text{ V}$ , Ta = 25°C)

#### Power on Operation (Reference Only)

# **ATA10 Series**

#### Sector Read

#### Sector Write

### **AC Characteristics**

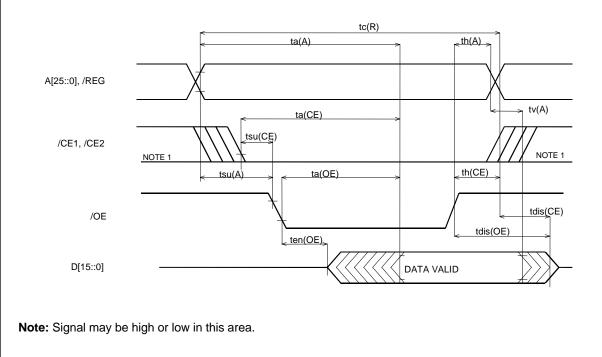

#### **Read Timing Parameters**

|                       |                                    | 250ns |     |      |

|-----------------------|------------------------------------|-------|-----|------|

| SYM<br>(PCMCIA)       | Parameter                          | Min   | Max | Unit |

| T <sub>C</sub> (R)    | Read Cycle Time                    | 250   |     | ns   |

| t <sub>a</sub> (A)    | Address Access Time                |       | 250 | ns   |

| t <sub>a</sub> (CE)   | Card Enable Access Time            |       | 250 | ns   |

| t <sub>a</sub> (OE)   | Output Enable Access Time          |       | 150 | ns   |

| t <sub>su</sub> (A)   | Address Setup Time                 | 30    |     | ns   |

| t <sub>su</sub> (CE)  | Card Enable Setup Time             | 0     |     | ns   |

| t <sub>h</sub> (A)    | Address Hold Time                  | 20    |     | ns   |

| t <sub>h</sub> (CE)   | Card Enable Hold Time              |       | 20  | ns   |

| t <sub>v</sub> (A)    | Output Hold from Address<br>Change |       | 0   | ns   |

| t <sub>dis</sub> (CE) | Output Disable Time from CE#       |       | 100 | ns   |

| t <sub>dis</sub> (OE) | Output Disable Time from OE#       |       | 100 | ns   |

| T <sub>en</sub> (CE)  | Output Enable Time from CE#        | 5     |     | ns   |

| T <sub>en</sub> (OE)  | Output Enable Time from OE#        | 5     |     | ns   |

Note: AC timing diagrams and characteristics are guaranteed to meet or exceed PCMCIA 2.1 specifications.

#### **Read Timing Diagram**

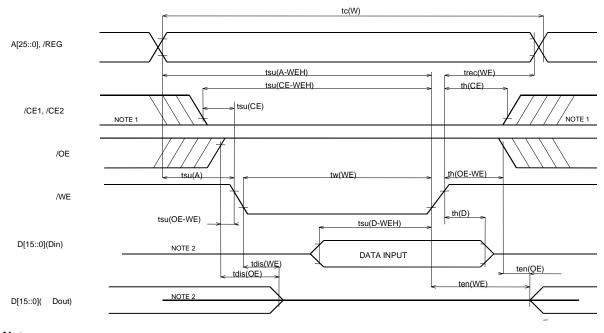

### **Write Timing Parameters**

|                          |                                 | 250ns | 5   |      |

|--------------------------|---------------------------------|-------|-----|------|

| SYM<br>(PCMCIA)          | Parameter                       | Min   | Max | Unit |

| t <sub>C</sub> (W)       | Write Cycle Time                | 250   |     | ns   |

| t <sub>w</sub> (WE)      | Write Pulse Width               | 150   |     | ns   |

| t <sub>su</sub> (A)      | Address Setup Time              | 30    |     | ns   |

| t <sub>su</sub> (A-WEH)  | Address Setup Time for WE#      | 180   |     | ns   |

| t <sub>su</sub> (CE-WEH) | Card Enable Setup Time for WE#  | 180   |     | ns   |

| t <sub>su</sub> (D-WEH)  | Data Setup Time for WE#         | 80    |     | ns   |

| t <sub>h</sub> (D)       | Data Hold Time                  | 30    |     | ns   |

| t <sub>rec</sub> (WE)    | Write Recover Time              | 30    |     | ns   |

| t <sub>dis</sub> (WE)    | Output Disable Time from WE#    |       | 100 | ns   |

| t <sub>dis</sub> (OE)    | Output Disable Time from OE#    |       | 100 | ns   |

| t <sub>en</sub> (WE)     | Output Enable Time from WE#     | 5     |     | ns   |

| T <sub>en</sub> (OE)     | Output Enable Time from OE#     | 5     |     | ns   |

| t <sub>su</sub> (OE-WE)  | Output Enable Setup from WE#    | 10    |     | ns   |

| t <sub>h</sub> (OE-WE)   | Output Enable Hold from WE#     | 10    |     | ns   |

| t <sub>su</sub> (OE)     | Card Enable Setup Time from OE# | 0     |     | ns   |

| t <sub>h</sub> (CE)      | Card Enable Hold Time           | 20    |     | ns   |

Note: AC timing diagrams and characteristics are guaranteed to meet or exceed PCMCIA 2.1 specifications.

#### Write Timing Diagram

#### Notes:

- 2. When the data I/O pins are in the output state, no signals shall be applied to the

- data pins (D15 D0) by the host system. June 2000 Rev. 5 - ECO #12901

<sup>1.</sup> Signal may be high or low in this area.

7P016ATA1000C15

**ATA10 Series**

|                    | 016ATA1000C15 <u>C</u> 9 | <u>995 9915</u>                                                                                        |

|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------|

| EDI                |                          | Date code                                                                                              |

|                    |                          | Lot code / trace number                                                                                |

|                    |                          | Part number                                                                                            |

|                    |                          | <u>Com</u> pany Name                                                                                   |

| some products will |                          | ny name/acronym (EDI). During our transition period<br>acronym (WED). Starting October 2000 all PCMCIA |

Card access time

**Temperature range**

**Packaging option**

Industrial

**Card capacity**

16MB

**Card technology**

C Commercial  $0^{\circ}$ C to  $+70^{\circ}$ C

**Card family and version**

150ns

250ns

-40°C to +85°C

Standard, type 1

Standard PCMCIA

FLASH

SRAM

Ruggedized PCMCIA

- See Card Family and Version Info. for details (next page)

15

25

I

00

016

Ρ

R

7

8

PC card

# **7P** XXX **ATA** YY SS T ZZ

#### where

| XXX:       | 008                                          | 8MB                                                                                                                                                       |                                                                               |

|------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|            | 016                                          | 16MB                                                                                                                                                      |                                                                               |

|            | 032                                          | 32MB                                                                                                                                                      |                                                                               |

|            | 048                                          | 48MB                                                                                                                                                      |                                                                               |

|            | 064                                          | 64MB                                                                                                                                                      |                                                                               |

|            | 080                                          | 80MB                                                                                                                                                      |                                                                               |

|            | 096                                          | 96MB                                                                                                                                                      |                                                                               |

|            | 112                                          | 112MB                                                                                                                                                     |                                                                               |

|            | 128                                          | 128MB                                                                                                                                                     |                                                                               |

|            | 192                                          | 192MB                                                                                                                                                     |                                                                               |

|            | 224                                          | 224MB                                                                                                                                                     |                                                                               |

|            | 256                                          | 256MB                                                                                                                                                     |                                                                               |

|            | 320                                          | 320MB                                                                                                                                                     |                                                                               |

|            | 384                                          | 384MB                                                                                                                                                     |                                                                               |

|            | 448                                          | 448MB                                                                                                                                                     |                                                                               |

|            | 510                                          | 512MB                                                                                                                                                     |                                                                               |

|            | 512                                          | 512WID                                                                                                                                                    |                                                                               |

| YY:        | 512<br>10                                    | Standard, 5V Only: (Cor                                                                                                                                   | ntroller type = MX)                                                           |

| YY:<br>SS: |                                              |                                                                                                                                                           | ntroller type = MX)<br>Type I                                                 |

|            | 10                                           | Standard, 5V Only: (Cor                                                                                                                                   |                                                                               |

|            | 10<br>00                                     | Standard, 5V Only: (Cor<br>WEDC FLASH Logo,                                                                                                               | Туре І                                                                        |

|            | 10<br>00<br>01                               | Standard, 5V Only: (Cor<br>WEDC FLASH Logo,<br>Blank Housing,                                                                                             | Type I<br>Type I                                                              |

|            | 10<br>00<br>01<br>02                         | Standard, 5V Only: (Cor<br>WEDC FLASH Logo,<br>Blank Housing,<br>Blank Housing,                                                                           | Type I<br>Type I<br>Type I Recessed                                           |

|            | 10<br>00<br>01<br>02<br>03                   | Standard, 5V Only: (Cor<br>WEDC FLASH Logo,<br>Blank Housing,<br>Blank Housing,<br>WEDC FLASH Logo,                                                       | Туре I<br>Туре I<br>Туре I Recessed<br>Туре II                                |

|            | 10<br>00<br>01<br>02<br>03<br>04             | Standard, 5V Only: (Cor<br>WEDC FLASH Logo,<br>Blank Housing,<br>Blank Housing,<br>WEDC FLASH Logo,<br>Blank Housing,                                     | Type I<br>Type I<br>Type I Recessed<br>Type II<br>Type II                     |

|            | 10<br>00<br>01<br>02<br>03<br>04<br>05       | Standard, 5V Only: (Cor<br>WEDC FLASH Logo,<br>Blank Housing,<br>Blank Housing,<br>WEDC FLASH Logo,<br>Blank Housing,<br>Blank Housing,                   | Type I<br>Type I<br>Type I Recessed<br>Type II<br>Type II<br>Type II Recessed |

| SS:        | 10<br>00<br>01<br>02<br>03<br>04<br>05<br>14 | Standard, 5V Only: (Cor<br>WEDC FLASH Logo,<br>Blank Housing,<br>Blank Housing,<br>WEDC FLASH Logo,<br>Blank Housing,<br>Blank Housing,<br>Blank Housing, | Type I<br>Type I<br>Type I Recessed<br>Type II<br>Type II<br>Type II Recessed |

### **ATA10 Series**

#### **Revision History:**

| rev level | description                                                                                                       | date          |

|-----------|-------------------------------------------------------------------------------------------------------------------|---------------|

| rev 0     | initial release                                                                                                   | June 1, 1998  |

| rev 1     | Logo change<br>New card capacity                                                                                  | May 27, 1999  |

| rev 2     | New flowcharts added<br>New timing diagrams<br>added                                                              | Sep 10, 1999  |

| rev 3     | New form factor<br>options added<br>New Flowcharts added<br>New current waveforms<br>added<br>Register list added | Oct. 18, 1999 |

| rev 4     | Max capacity change to 512MB                                                                                      | Dec 19, 1999  |

| rev 5     | Timing corrections on Pgs 21 & 22.<br>Page 23 added, Page Header<br>changed                                       | June 2, 2000  |

## White Electronic Designs Corporation

One Research Drive, Westborough, MA 01581, USA

tel: (508) 366 5151

fax: (508) 836 4850

www.whiteedc.com

WHITE ELECTRONIC DESIGNS